# **CLASS 8&9**

## STABILITY OF BJT BIASING CIRCUITS, BJT AS A SWITCH, SMALL-SIGNAL EQUIVALENT CIRCUIT OF THE BJT AND FETs

### PARAMETERS THAT CAN CHANGE THE Q-POINT

• The DC current gain of the CE,  $\beta_{DC}$  or  $h_{FE}$ , for one type of transistor is typically available in a large range,  $h_{FE} = 50$  to 300. The large range of  $\beta_{DC}$  or  $h_{FE}$  influences the transistor's biasing as  $I_C = \beta_{DC} I_B$  (if the leakage current is neglected). If  $I_B$  is fixed and  $\beta_{DC}$  is varied,  $I_C$  will also change.  $I_{CQ}$  and  $V_{CEQ}$  will change, i.e. the operating point changes.

The transistor might not be operating in the active region.

• Temperature can also change the operating point as the temperature changes the number of minority carriers. This can be seen from the expressions:

$$\mathbf{I}_{\mathrm{C}} = \beta_{\mathrm{DC}} \mathbf{I}_{\mathrm{B}} + \mathbf{I}_{\mathrm{CEO}} = \alpha_{\mathrm{o}} \mathbf{I}_{\mathrm{E}} + \mathbf{I}_{\mathrm{CBO}}$$

where the  $I_{CEO}$  and  $I_{CBO}\,\,$  are the minority carrier currents.

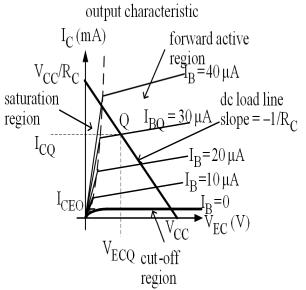

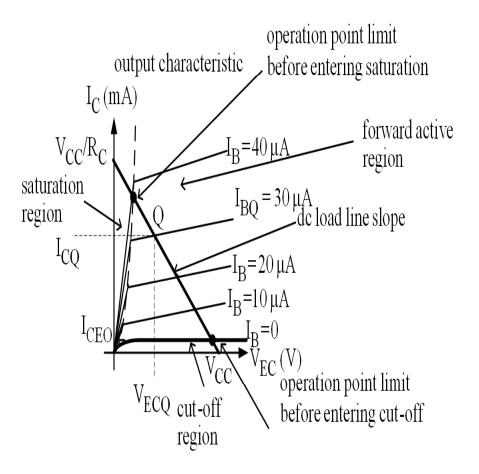

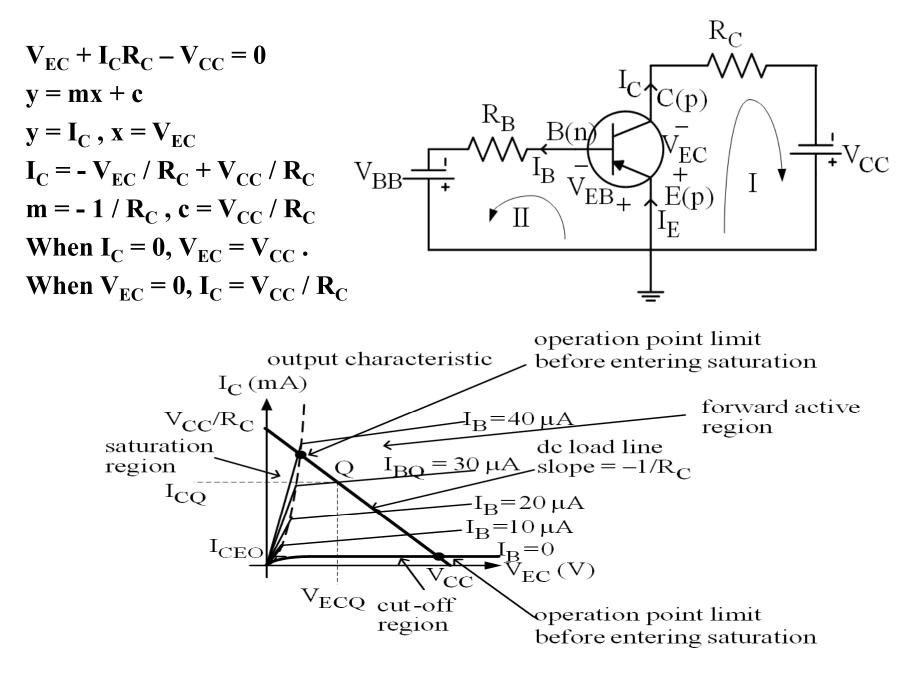

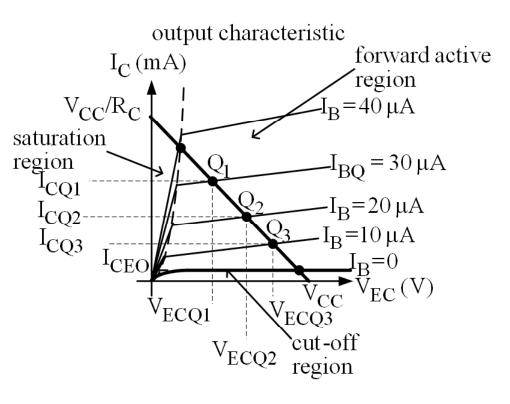

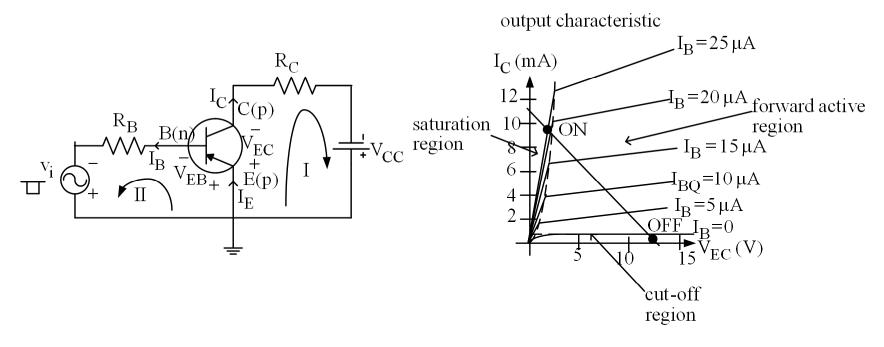

- The dc load line can be determined by analyzing the transistor's circuit.

- The transistor load line is linear and is in the form:

y = mx + c

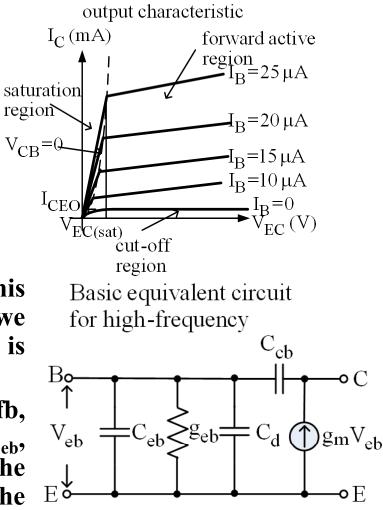

By looking at the output characteristic of the CE,

$$\mathbf{y} = \mathbf{I}_{\mathbf{C}}$$

$\mathbf{x} = \mathbf{V}_{\mathbf{EC}}$

m = slope of the load line c = intersection of the loadline with the I<sub>C</sub> axis. The load line intersects the V<sub>EC</sub> axis at I<sub>C</sub> =0.

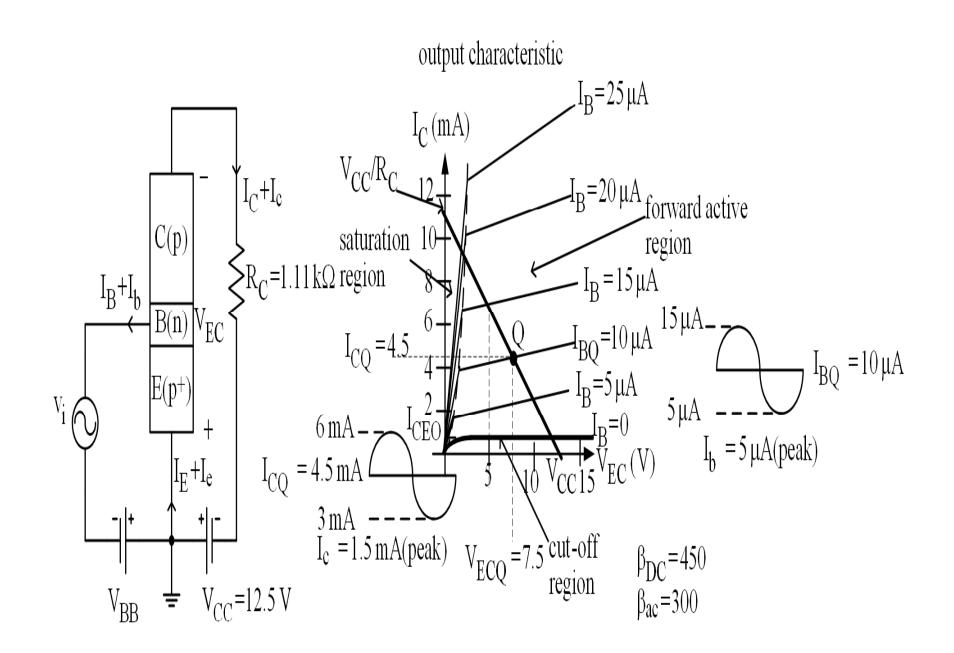

• When  $I_{BQ}$  is known, the value of  $I_{CQ}$  and  $V_{ECQ}$  can be determined by the intersection of the dc load line with the  $I_{BQ}$  curve.

- If the quiescent B current is  $I_{BQ}$ , then the operation point is  $Q_1$  with output C current,  $I_{CQ1}$ , and E-C voltage,  $V_{ECQ1}$ .

- If the quiescent B current is 20  $\mu$ A, then the operation point is Q<sub>2</sub> with output C current, I<sub>CQ2</sub>, and E-C voltage, V<sub>ECQ2</sub>.

- If the quiescent B current is 10  $\mu$ A, then the operation point is Q<sub>3</sub> with output C current, I<sub>CQ3</sub>, and E-C voltage, V<sub>ECQ3</sub>.

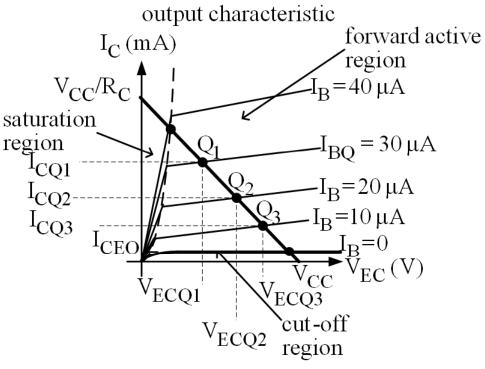

#### If inaccurate Q is chosen:

- Transistor can be driven into saturation region (if Q is too close to the saturation region)

- Transistor can be driven into cut-off region (if Q is too close to the cut-off region)

- Transistor can be driven into both saturation and cutoff region (the Q point might be at the centre but the signal is too large)

The result is a distorted signal at the output. This defeats the purpose of using the amplifier which is to have an amplified replica of the input signal at the output.

#### From Floyd, Electronic Devices, Sixth Edition.

Graphical load line illustration of a transistor being driven into saturation and/or cutoff.

## **DC BIASING CIRCUITS**

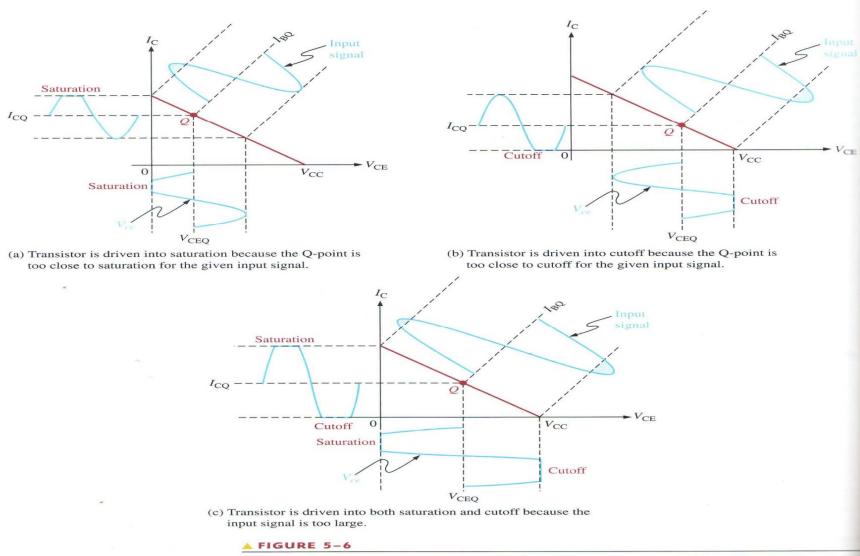

- 1. Fixed-current/Base biasing circuit Unstable

- 2. Collector-Base/Collector feedback biasing circuit Stable

- 3. Voltage division biasing circuit Stable and the most popular

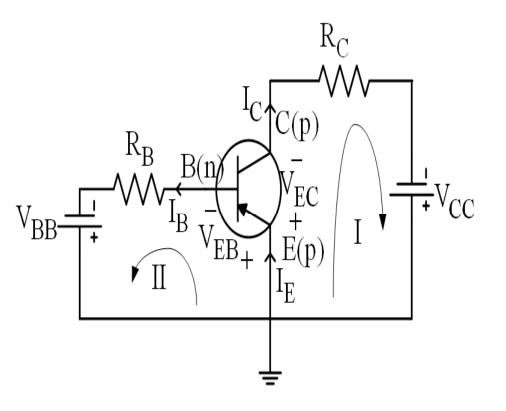

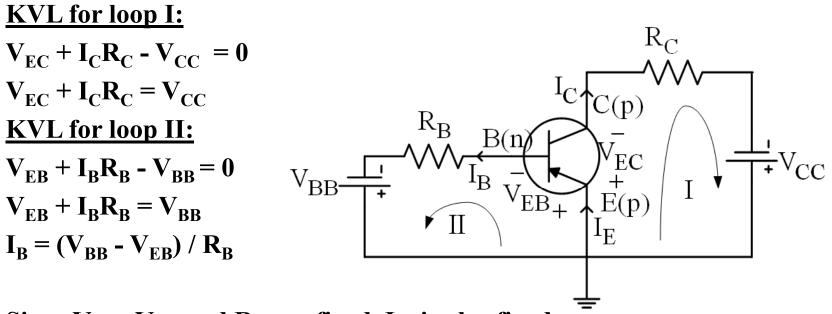

### **FIXED-CURRENT / BASE BIASING CIRCUIT**

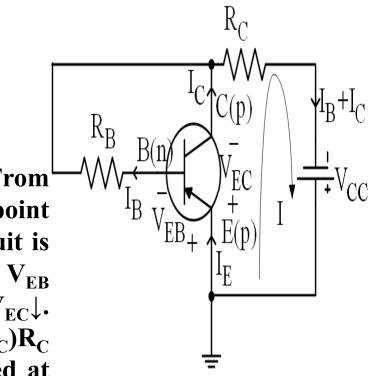

## KVL for loop I:

$\mathbf{V}_{\mathrm{EC}} + \mathbf{I}_{\mathrm{C}}\mathbf{R}_{\mathrm{C}} - \mathbf{V}_{\mathrm{CC}} = \mathbf{0}$  $\mathbf{V}_{\mathrm{EC}} + \mathbf{I}_{\mathrm{C}}\mathbf{R}_{\mathrm{C}} = \mathbf{V}_{\mathrm{CC}}$

$\frac{\text{KVL for loop II:}}{\text{V}_{\text{EB}} + \text{I}_{\text{B}}\text{R}_{\text{B}} - \text{V}_{\text{BB}} = 0}$  $\text{V}_{\text{EB}} + \text{I}_{\text{B}}\text{R}_{\text{B}} = \text{V}_{\text{BB}}$  $\text{I}_{\text{B}} = (\text{V}_{\text{BB}} - \text{V}_{\text{EB}}) / \text{R}_{\text{B}}$

Since  $V_{BB}$  ,  $V_{EB}$  and  $R_{B}$  are fixed,  $I_{B}\,$  is also fixed.

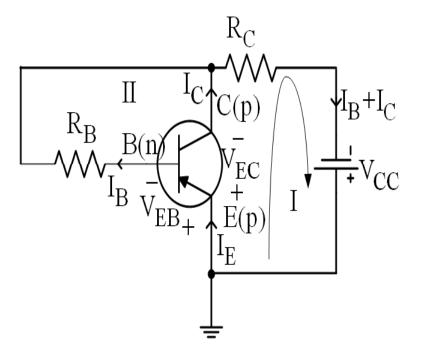

## COLLECTOR TO BASE / COLLECTOR FEEDBACK BIASING CIRCUIT

**<u>KVL of loop I:</u>**   $V_{EC} + (I_B + I_C)R_C - V_{CC} = 0$   $V_{EC} + (I_B + I_C)R_C = V_{CC}$   $V_{EC} + (I_B + \beta_{DC}I_B)R_C = V_{CC}$  if the minority carrier leakage current is neglected.

$\frac{\text{KVL of loop II:}}{\text{V}_{\text{EB}} + \text{I}_{\text{B}}\text{R}_{\text{B}} - \text{V}_{\text{EC}} = 0}$  $\text{I}_{\text{B}} = (\text{V}_{\text{EC}} - \text{V}_{\text{EB}}) / \text{R}_{\text{B}}$

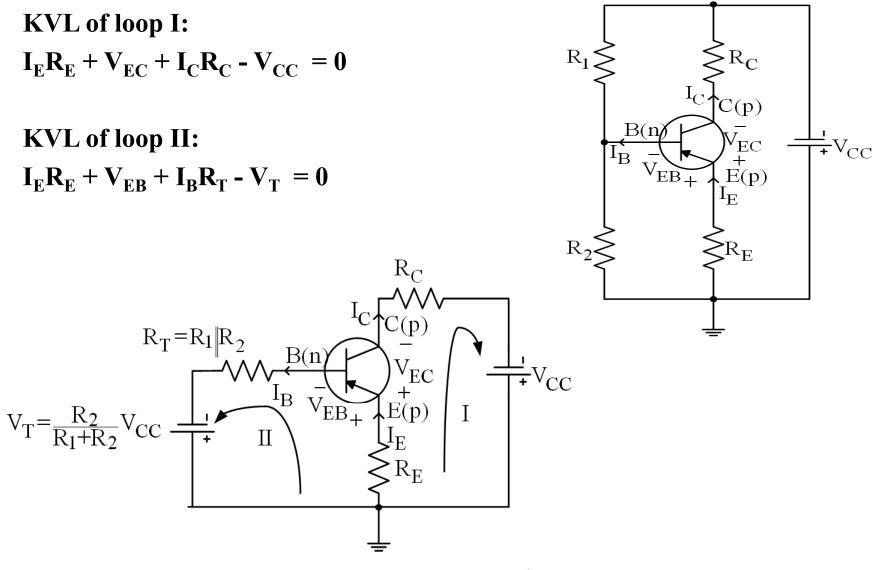

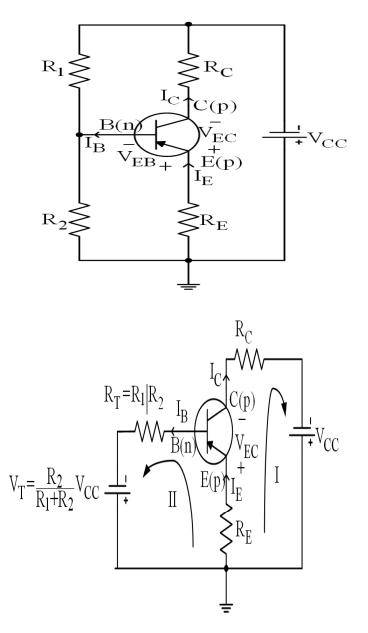

## **VOLTAGE DIVISION BIASING CIRCUIT**

## **STABILITY OF THE BIASING CIRCUITS**

Since  $V_{BB}$ ,  $V_{EB}$  and  $R_B$  are fixed,  $I_B$  is also fixed.

If  $T\uparrow$ ,  $I_C\uparrow$ ; hence,  $V_{EC}\downarrow$ . The Q point will change as the Q point of the CE circuit is  $I_{CQ}$  and  $V_{ECQ}$ .

As the  $I_B$  is fixed, this condition does not help in stabilizing the Q point of the circuit when changes occur. Thus, fixed-current biasing circuit is said to be less stable in terms of its biasing performance.

KVL of loop I:

$V_{EC} + (I_B + I_C)R_C = V_{CC}$ (1) <u>KVL of loop II:</u>

$I_{B} = (V_{EC} - V_{EB}) / R_{B}$  (2) From  $I_{C} = \beta_{DC} I_{B} + I_{CEO}$ ,  $T\uparrow$  then  $I_{C}\uparrow$ . From (1),  $V_{EC}\downarrow$  when  $I_{C}\uparrow$ . If this happens, the Q point will change as the Q point of the CE circuit is  $I_{CQ}$  and  $V_{ECQ}$ . However, from (2), since  $V_{EB}$ and  $R_{B}$  are fixed values,  $I_{B}$  will  $\downarrow$  when  $V_{EC}\downarrow$ . This condition will maintain the  $(I_{B}+I_{C})R_{C}$ term in (1). Hence,  $V_{EC}$  will be maintained at the quiescent value before the temperature change. Thus, collector feedback biasing circuit is said to be more stable in terms of its biasing performance.

**KVL of loop I:**

$I_E R_E + V_{EC} + I_C R_C = V_{CC}$ (1) KVL of loop II:

$I_E R_E + V_{EB} + I_B R_T = V_T$  $I_E R_E + I_B R_T = V_T - V_{EB}$ (2)

When  $T\uparrow$ , then  $I_C\uparrow$ .  $I_E$  will also  $\uparrow$  as  $I_C\approx \alpha I_E$ . From (2), since  $V_{EB}$ ,  $V_T$ ,  $R_E$  and  $R_T$  are fixed values, when  $I_E\uparrow$ , then  $I_B\downarrow$ . From  $I_C=\beta_{DC} I_B + I_{CEO}$ , when  $T\uparrow I_{CEO}\uparrow$  and will supposedly increase the  $I_C$  and consequently  $I_E$  However, this will make  $I_B\downarrow$ . Thus,  $I_C$  will be maintained. Therefore,  $I_B$  is helping to stabilize the circuit by maintaining the Q point. This circuit is the most popular amongst the 3 biasing circuits discussed.

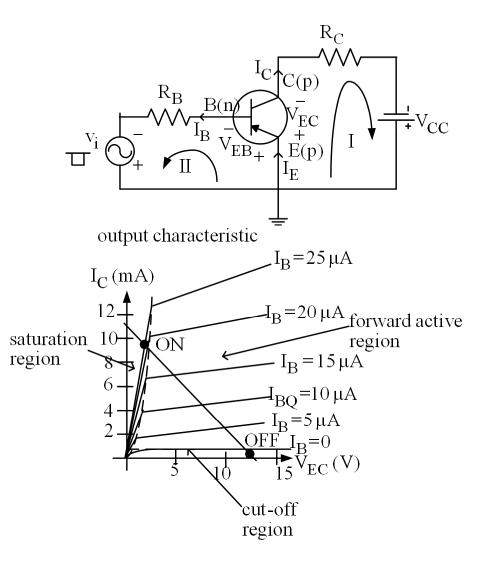

## **BJT AS A SWITCH**

- In digital applications, the transistors are normally utilized as switches. As a switch, I<sub>B</sub> is used to convert I<sub>C</sub> from OFF to ON.

- OFF condition: high voltage and low current

- ON condition: low voltage and high current

- Transistor is an o/c between E and C in the OFF condition.

- Transistor is a s/c between E and C in the ON condition.

- Hence, the transistor's operation is like a switch.

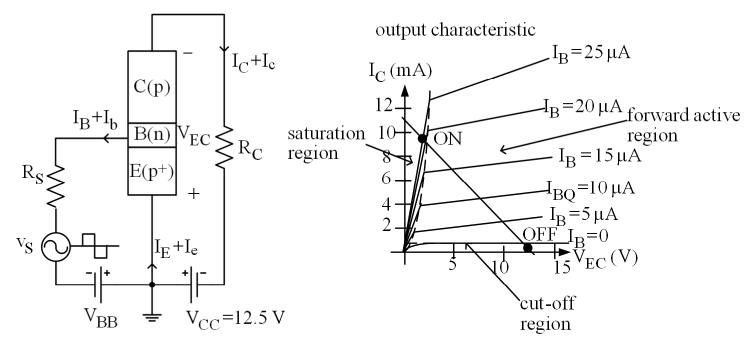

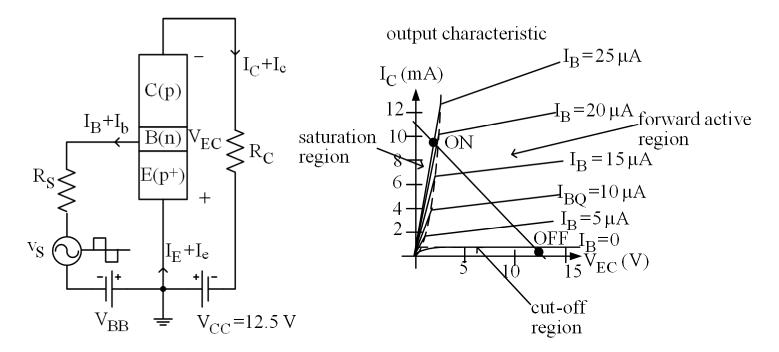

### **CUT-OFF**

• If  $|v_i|$  is < 0.7, the E-B junction will let only a very small insignificant current to flow. Under this condition, the E-B junction is still considered as OFF.  $I_B = I_C = I_E \approx 0$ .  $V_{EC} = V_{CC}$ . B-C junction is also rb. The transistor is said to be in the cut-off condition (voltage is high, current is very small).

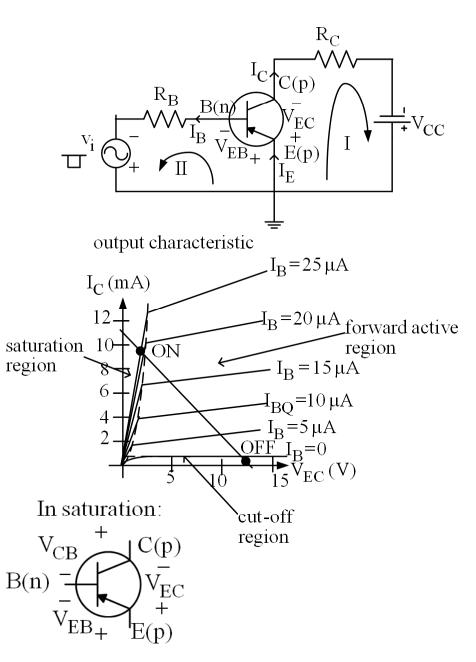

#### **SATURATION**

- If  $|v_i| \uparrow$ ,  $I_B \uparrow I_C \uparrow$  and  $V_{EC} \downarrow$  (from  $V_{EC} + I_C R_C = V_{CC}$ ). If the  $|V_{EC}| < 0.7$  V, the device will enter the saturation region as both E-B and B-C junctions are fb.

- Under this condition,  $|V_C| < |V_B|$ . The B-C junction will be fb as the C is more +ve than the B. The B-C junction can be fb by a forward voltage of 0.4 to 0.5 V. The forward voltage drop of the B-C junction is smaller than the forward voltage drop of the E-B junction (i.e. 0.7 V) because C is doped less than E.  $[V_o=(kT/q)ln(N_AN_D/n_i^2)].$

- This condition is called saturation as any increment in the  $I_B$  will only cause the  $I_C$  to increase by a small amount and therefore,  $V_{EC}$ will also decrease by a small amount.

- The minimum rb of the BC junction is when  $V_{BC} = 0$ .

- In the saturation region,  $\Delta I_C / \Delta I_B \neq \beta_{DC}$ .

- As the forward voltage drop of the B-C junction is in the range 0.4 V to 0.5 V, then

$V_{EB} - V_{CB} - V_{EC} = 0$ . Under this condition,  $V_{EC} = V_{EC(sat)} = 0.3 V$  to 0.2 V.

•  $\mathbf{V}_{CC} = \mathbf{V}_{EC(sat)} + \mathbf{I}_{C(sat)}\mathbf{R}_{C}$  $\mathbf{I}_{C(sat)} = [\mathbf{V}_{CC} - \mathbf{V}_{EC(sat)}]/\mathbf{R}_{C}$

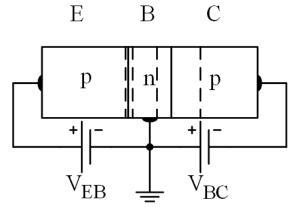

- BJT has 4 modes of operation, i.e. forward active, saturation, cut-off and inverted. The mode of operation is dependent on the biasing condition of the BE and BC junctions.

- In analogue circuits, transistors normally operate in the active mode.

- In digital circuits, all 4 modes might be involved.

- So far, we had seen the static (or DC) characteristics of the BJT. Now we will learn about the AC characteristics of the BJT when a small-signal voltage or current is superimposed on its DC signal. Small-signal means the peak AC voltage and current are smaller than their DC values.

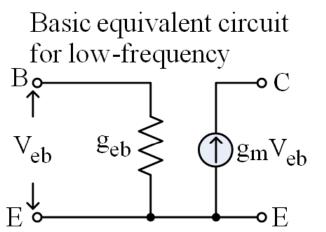

## SMALL-SIGNAL EQUIVALENT CIRCUIT OF BJT

•  $g_m = I_c/V_{eb}$  is the transconductance.

- $g_{eb} = I_b/V_{eb}$  is the i/p conductance. This conductance must be included as we are considering the current that is flowing through the fb E-B junction.

- At higher frequencies, when E-B is fb, there exist a depletion capacitance,  $C_{eb}$ , and diffusion capacitance,  $C_d$ . For the rb B-C junction, there exist only the depletion capacitance,  $C_{cb}$ .

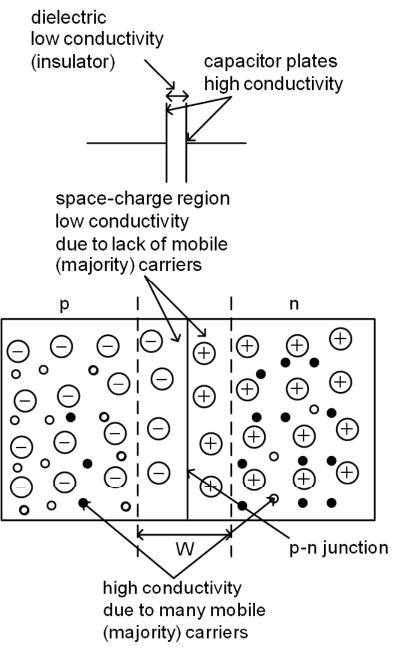

#### **Depletion capacitance:**

Independent of whether the junction is forward or reverse biased, there exist the depletion region both sides of the on junction. The p-depletion region-n is similar structure to the structure of the capacitor. Due to the depletion region, depletion capacitance, C<sub>i</sub>, exist.

$C_j=dQ/dV=dQ/(WdQ/\epsilon A)=\epsilon A/W$ (unit for  $C_j$  is F/cm<sup>2</sup>)

dQ = change of charge per unit area of the depletion layer.

dV = change of voltage applied.

A = cross-section area.

ε = permittivity of Si

**W** = width of the depletion region

### **Diffusion capacitance**

- When the p-n junction is fb, large current flows through the junction. This will result in many mobile carriers to be in the neutral B. The change in the mobile carriers corresponding to the change in the biasing voltage will result in the diffusion capacitance,  $C_d$ .

- $C_d = (Aq^2L_pp_{no}/kT)e^{qV/(kT)}$ where

$L_p$  = diffusion length of hole in the n material

$p_{no}$  = equilibrium hole density in the n